发布时间:2017年6月21日

特约作者:Ray Fontaine

在IISW论文提交截止日期4月的时候,我们还没有收到索尼Xperia XZs 3层叠动眼摄像机。这项技术的发展已经在2017年的ISSCC上宣布了,我们确实及时得到了成果,可以用于演示材料(另见迪克詹姆斯的博客).IMX400项目的工作仍在继续,我们期待在几周内发布我们的报告。请欣赏第2部分,我们将讨论晶片到晶片互连和堆叠芯片的其他特性的趋势。

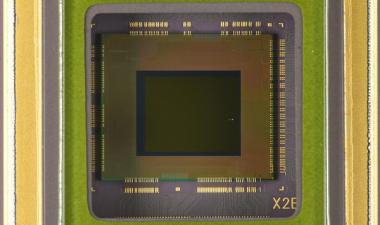

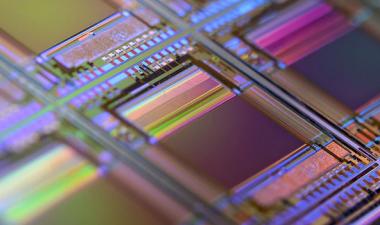

堆叠芯片图像传感器

低温晶片键合和各种晶片互连技术的发展是堆叠式图像传感器的关键实现因素。由背光CIS和混合信号图像信号处理器(ISP)组成的双模堆栈已经成为领先的智能手机相机芯片的主要配置。CIS部分可以被认为是只携带有源像素阵列的“哑”芯片。大部分的信号链和数字处理被划分到ISP和系统应用处理器上。

| 芯片供应商 | 一年 | 堆叠CIS铸造/ Gen。 | 堆叠ISP铸造/ Gen。 | |||

|---|---|---|---|---|---|---|

| 索尼 | 2013 | 索尼90 nm. | 索尼65纳姆 | |||

| 索尼 | 2014 | 索尼90 nm. | 台积电40海里 | |||

| 索尼 | 2016 | 索尼90 nm. | 台积电28 nm | |||

| omnivision. | 2015 | XMC 65 NM. | XMC 65 NM. | |||

| omnivision. | 2016 | 台积电65纳米 | 台积电65纳米 | |||

| 三星 | 2015 | 三星65纳米 | 三星65纳米 | |||

| 三星 | 2016 | 三星65纳米 | 三星28 nm hkmg | |||

| 索尼 | globalfoundries 2017 |

|

||||

表2。值得注意的堆叠芯片CIS/ISP配置

堆叠芯片制造技术趋势

堆叠结构背光CIS芯片最近的制造趋势似乎稳定在90/65纳米制程世代。虽然最近在1.0µm的像素结构中观察到65 nm以下的加工,以促进更窄的W孔径网格金属,但似乎没有进一步扩大CIS芯片技术一代的驱动因素。三星的28纳米高k金属栅工艺目前用于堆叠ISP [14], ISP的扩展趋势预计将继续向最新的先进CMOS技术一代发展。

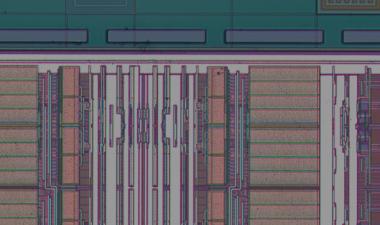

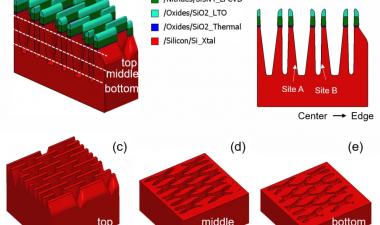

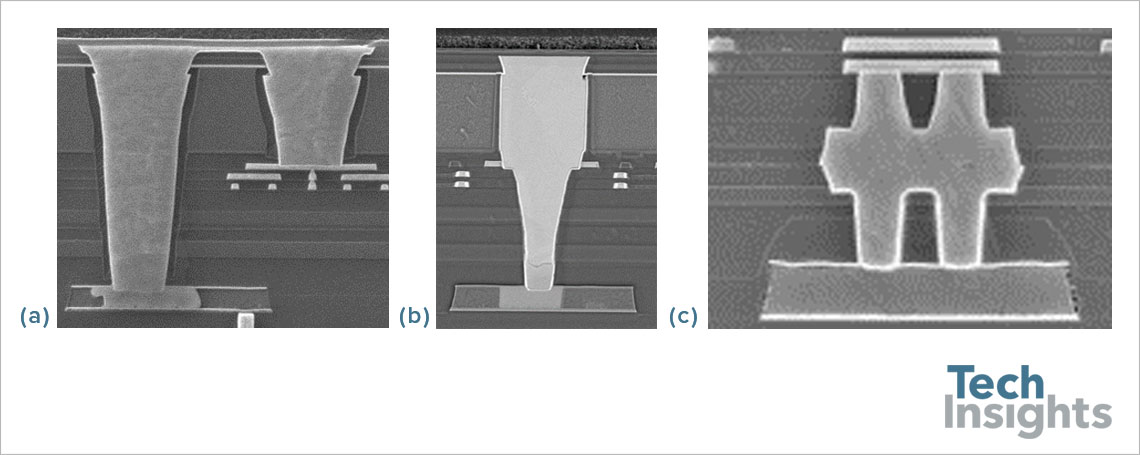

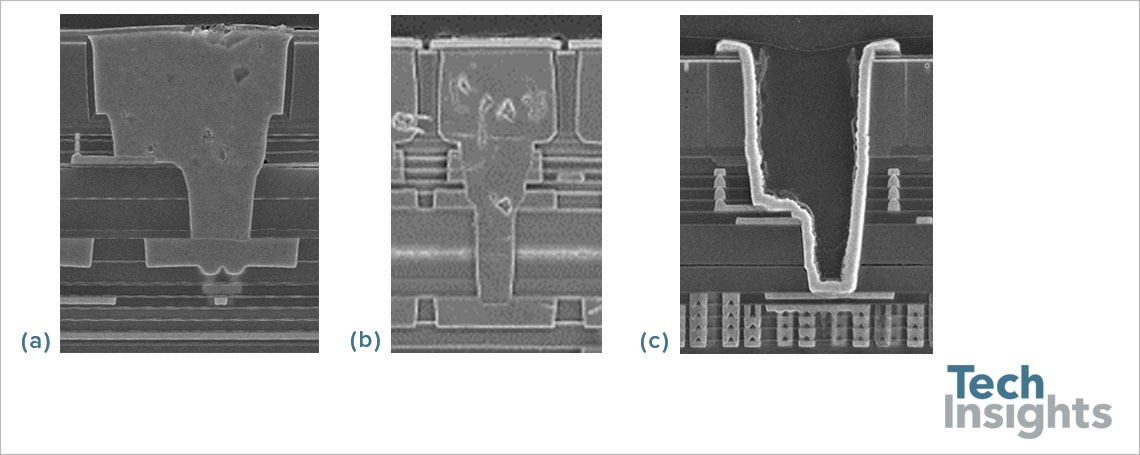

图1所示。索尼1级双TSV (a), 2级统一TSV (b), 1级DBI (c)

图2. Omnivision第1 Gen。对接TSV(A),第2 Gen。统一TSV(b),三星对接TSV(C)

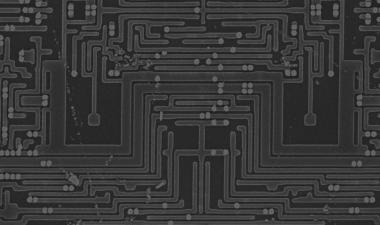

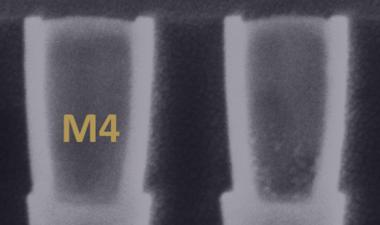

b .薄片互连

索尼是第一个将堆叠式CIS芯片推向市场的公司,最初在2013年实现了同质晶片与晶片键合(氧化键合)和通过硅通道(tsv),随后在2016年实现了Cu-to-Cu混合键合,也被称为Cu2Cu键合或DBI[18,19]。第一代TSV部署在有源像素阵列的上方和两侧,具有双TSV结构,用于1.12µm一代像素阵列的行/列互连。一个浅的、充铜的TSV接触金属1 CIS金属垫的背面,一个深的、充铜的TSV接触顶部金属Al ISP垫,最后通过平面铜金属带实现互连。双TSV结构为矩形结构,放置在6.0 μ m × 9.0 μ m正交间距[20]上。

2015年,TSony通过引入单一或“统一”的结构简化了TSV工艺流程,该结构通过一个圆柱形垂直互连[21]连接CIS和ISP起落架。这些结构被放置在9.1µm的最小正交间距上,尽管TSV行与相邻行有半间距交错。

OmniVision首次观察到的堆叠芯片是在PureCel-S平台上与foundry合作伙伴XMC制作的,具有“对接”TSV结构,其中单个宽TSV连接CIS和ISP衬垫结构。在1.12 μ m像素生成芯片上使用的矩形结构具有5.2 μ m × 9.9 μ m正交pitch[22]。后来,OmniVision采用了统一的TSV结构,用于其1.0 μ m像素级PureCelPlus-S芯片,由代晶商台积电(TSMC)制造。这些结构放置在4.0µm × 4.1µm正交沥青[10]上。

所观察到的制作中的三星堆叠芯片还具有对接的TSV结构,而是使用基于W基的TSV窗衬管垂直互连。将在1.12μm像素生成芯片上的第一代三星TSV置于8.8μm×9.6μm正交间距[23]。

索尼最近改变了其互连策略,最初将DBI作为TSV阵列的替代。这种DBI实现的特点是,活动DBI垫位于被tsv占用的相同区域,虚拟DBI垫覆盖了大部分有源像素阵列和外围区域。目前生产DBI的最先进技术是将3.0 μ m宽的方形垫放置在6.0 μ m正交节距上。据报道,DBI音高为1.6µm[24],预计未来的DBI芯片将实现逐像素互连。

定期,简洁地分析大批量成像和新兴应用

参考

[1] Fujifilm新闻稿,7月21日。

[2] " fujifilms3961 Die标记12.0 MP, 1.6 μm像素尺寸CCD图像传感器fujifilfinepix Z800EXR聚焦技术分析(FTA)报告",知识产权-1009-801-01,-03,-04,-05,2010年10月。

[3]尼康新闻发布会,2011年9月

[4]“APTINA MT9J007C1HS 12百万像素(10.1百万像素有效)CMOS图像传感器,具有来自尼康V1 Camera Imager Process Review的DR-PIX™技术”,IPR-1110-804,2011年12月。[5]佳能EOS 650D新闻稿,君。2012年。

[6] " Canon LC1270 18.0 MP, 4.3 μm Pixel Size, APS-C Format CMOS Image Sensor from Canon EOS Rebel T4i (EOS 650D/EOS Kiss X6i) ",知识产权-1206-802,2012年8月。

[7] " Sony IMX270, Micro Four Thirds, 20.4 MP Resolution, 3.3µm Pixel Pitch,正面照明" Live MOS " CMOS Image Sensor from Olympus OM-D E-M1 Mark II MILC ", DEF-1703-802, 2017年4月

[8]富士州新闻稿,2013年1月。

[9]“TOSHIBA TCM5112CL CMOS图像传感器来自Fujifilm X20设备要素摘要”,DEF-1311-803,2013年11月。

[10] " OmniVision OV16880, 1/3.06 "格式,16mp分辨率,1.0 μm像素间距堆叠(PureCel Plus-S)背光CMOS图像传感器",DEF-1606-804, 2016年8月。

[11]索尼Xperia Z5产品页面,2015年10月。

[12]佳能EOS 70D新闻稿,2013年7月。

[13]三星新闻稿,2016年3月。

[14] " Samsung S5K2L1, 1/2.6 "格式,12mp分辨率,1.4 μm像素间距背光堆叠ISOCELL CMOS图像传感器,三星Galaxy S7(型号SM-G930FD) ", DEF-1603-804, 2016年4月。

[15]“SONY IMX260 12 MP,1.4μm像素间距堆叠BI CIS,具有来自三星Galaxy S7 Edge后面的Camera Imager Process Revice评论的DBI和全芯片PDAF,”2016年5月16日,IPR-1603-802“。

[16]“索尼12MP分辨率,1.0μm像素生成堆叠(EXMOR RS)从iPhone 7加电视相机堆积的反光CMOS图像传感器”,DEF-1612-801,2017年1月。

[17] OPPO R9S着陆页,2016年10月。

[18] Kagawa,et。AL,“具有先进的CU2C2混合键合的”新型堆叠CMOS图像传感器“ISSCC2017。2017年2月。

[19] Invensas公司网站,2017年4月。

[20] " Sony ISX014 1/4英寸8mp, 1.12 μm Pixel Size Exmor RS Stacked Back Illuminated CIS Imager Process Review ", IPR-1302-801, 2013年3月。

[21]“SONY IMX278 13.0 MP EXMOR RS™RGBW堆叠的BI CMOS图像传感器从华为P8成像过程中提取”,IPR-1505-801,JUL。2015。

[22]“Omnivision OV23850 PureCel-S1.12μm像素,23.8MM堆叠CMOS图像传感器从Gionee GN9008”,Def-1508-802,2015年9月。

[23]“三星S5K3M2 13 MP堆叠,来自Vivo X5Pro的Isocell CMOS图像传感器”,DEF-1507-801,Jul。2015。

[24] P. Enquist,“堆叠图像传感器-新的图像传感器标准”,2015年图像传感器欧洲,2015年3月。

[25]“意法半导体5 MP, 1.4 μm像素间距CMOS图像传感器(5953BA模具标记)成像器工艺审查”,知识产权-1003-802,2010年4月。

[26]“SONY IMX147 20 MP,1.2μm像素音高回来照亮(EXMOR R)CMOS图像传感器,来自索尼网络HX300数字紧凑型摄像头”,IPR-1307-801,2013年9月。

[27]“三星S5K3P3SX 16 MP,1.0μm像素间距堆叠BSI Full Isocell CIS来自三星Galaxy A8 Smartphone Primary Camera Imager Process Review”,IPR-1509-801,2016年1月。