Posted: June 14, 2017

Contributing Authors: Jeongdong Choe, Senior Technical Fellow

三星已经开始批量生产了他们的前10名NM级DRAM产品,我们已经拿到了这个机会分析并比较了前几代25纳米和20纳米DRAM产品。在我们的分析过程中,我们发现了技术节点是18 nm,我们认为是用于设计活动模式的最小半间距。

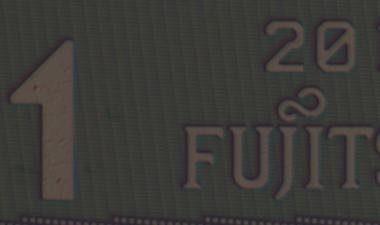

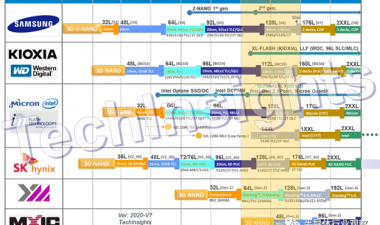

三星18纳米8 GB DRAM模具有0.189 GB / mm2. Compared to their 20 nm 8 Gb die, memory density has increased by 32.8%, while the cell size (0.0026 µm2)减少了21.2%。图1显示了Samsung,SK Hynix和Micron 30 NM类,20nm级和10nm级DRAM产品的DRAM模具尺寸和内存密度的比较。

图1. Samsung,SK Hynix和Micron的DRAM模具尺寸和内存密度的比较。

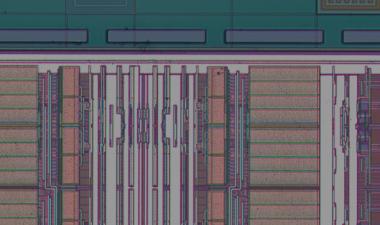

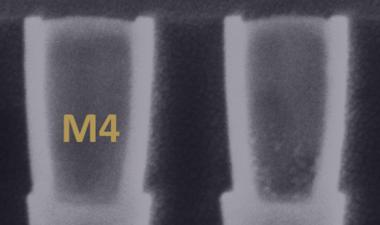

我们认为三星18 nm DRAM最具创新性方面之一是10纳米级的图案化技术。首次,三星成功开发并实施了18纳米DRAM产品的QPT(四倍图案化技术),包括DDR4,LPDDR4和LPDDR4X。使用48nm字体沥青和54nm位线间距,而主动间距为36nm,这意味着通过QPT集成有源模式。该技术已被用于1Y NM NAND技术,特别是15 nm(东芝/ SanDisk)和14 nm(三星)2D平面NAND门(CG / FG)图案化。DPT(双图案化技术)已用于2D平面1X和1Y NM NAND主动和位线图案。由于QPT成熟,三星可以加快开发下一个DDR5,LPDDR5和GDDR6产品的1Y NM(15nm)DRAM的时间。

更新!三星的防保险丝技术在18纳米DRAM上发现:使用的公斤2T-Cell技术

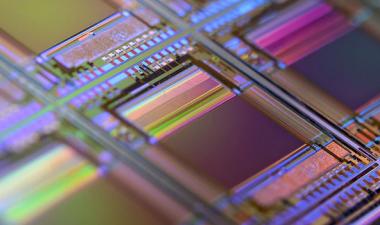

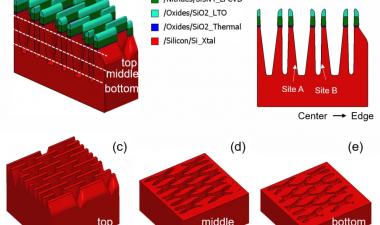

对于蜂窝型电容器结构,已经使用了超薄和非常均匀的Zro / Alzro双层高k电介质。利用以前的20 nm级DRAM技术,介电层在底部比底部较厚,使电容器似乎是倒置锥体。三星通过超细介电沉积技术开发了一种新的材料/过程,成功地使介电层的厚度均匀地均匀地到几埃。这种技术突破允许前10名NM级DRAM的诞生,具有高性能和可靠性。从我们对三星18 NM DRAM电容器结构的分析,1.06nm EOT(电氧化物厚度),1.77mV / cm(ZRO)和7.4FF /电池电容可以在1.2V,300k。

Download product information on Samsung 18nm DDR and LPDDR4X

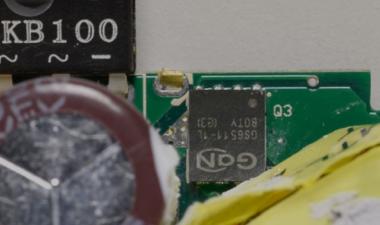

我们的产品信息包括:三星K3UH5H50MM-NGCJ(LPDDR4X移动SDRAM)和K4A8G085WC-BCRC(DDR4)