逻辑分析博客

高通双源骁龙8(+)Gen1 SOC

TechInsights证实台积电N4是一个真正的光学收缩N5节点

李泽楷

约翰·博伊德

在最近的记忆中,高通第一次与三星(4LPX)和台积电(N4)同时采购骁龙8(+)Gen1 SoC。这使得我们TechInsights能够比较两个不同铸造厂制造的共同设计。

我们之前的报告显示,台积电的N4E工艺(用于Mediateck的Dimensity 9000的台积电N4工艺的早期版本)带有掩模减少但没有收缩。你可能想知道台积电的N4工艺是否真的是N5的光学收缩?现在,我们有了答案:

在我们最近发布的关于台积电N4上的骁龙8(+)Gen1 SoC的First Look报告中,我们确认了制造骁龙8(+)Gen1 SoC的台积电N4技术是从台积电N5节点上真正的光学收缩。

比特单元进一步缩小(最小缩小4%),而其他技术特征与前几代技术共享,并在techhinsights的First Look报告中总结(现在对我们的订阅者开放)。

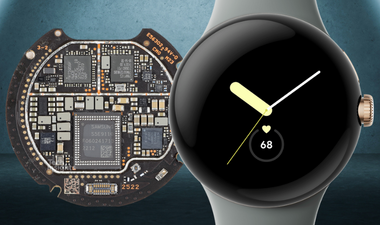

图1:高通骁龙8 Gen 1 SoC的平面图

图2:高通骁龙8+ Gen1 SoC的平面图

图3:通过高密度库逻辑块的透射电镜截面

图4:通过高密度库逻辑块的透射电镜截面

想知道更多吗?订阅TechInsights逻辑过程频道查看完整报告。成为订阅用户后,你亦可浏览我们的网页:

- 先看看用三星4LPX技术制造的骁龙8 Gen1的报告

- 采用三星4LPX技术制造的骁龙8 Gen1的先进CMOS Essentials报告

- 三星Exynos 2200 4LPE(一个主要的工艺节点变化与基音尺度)和4LPX(本质上是一个5LPE技术)技术的比较